Low Power Design Examples | Block representation in a hierarchical UPF multi-voltage IC design

Di: Samuel

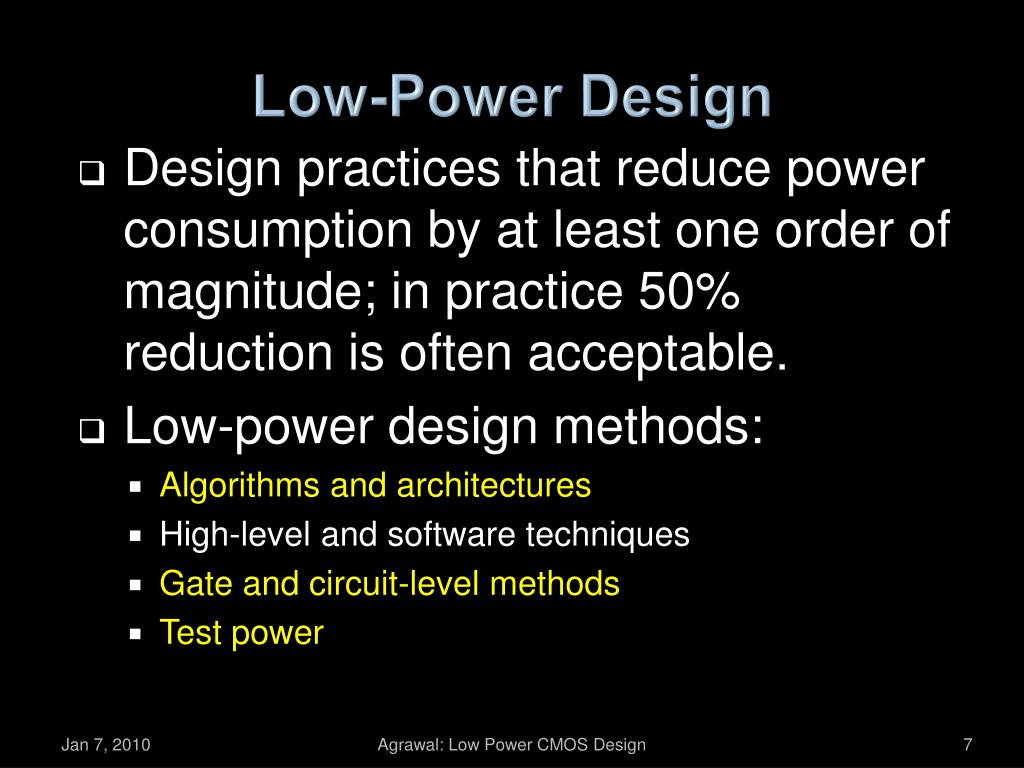

What is a low power design?

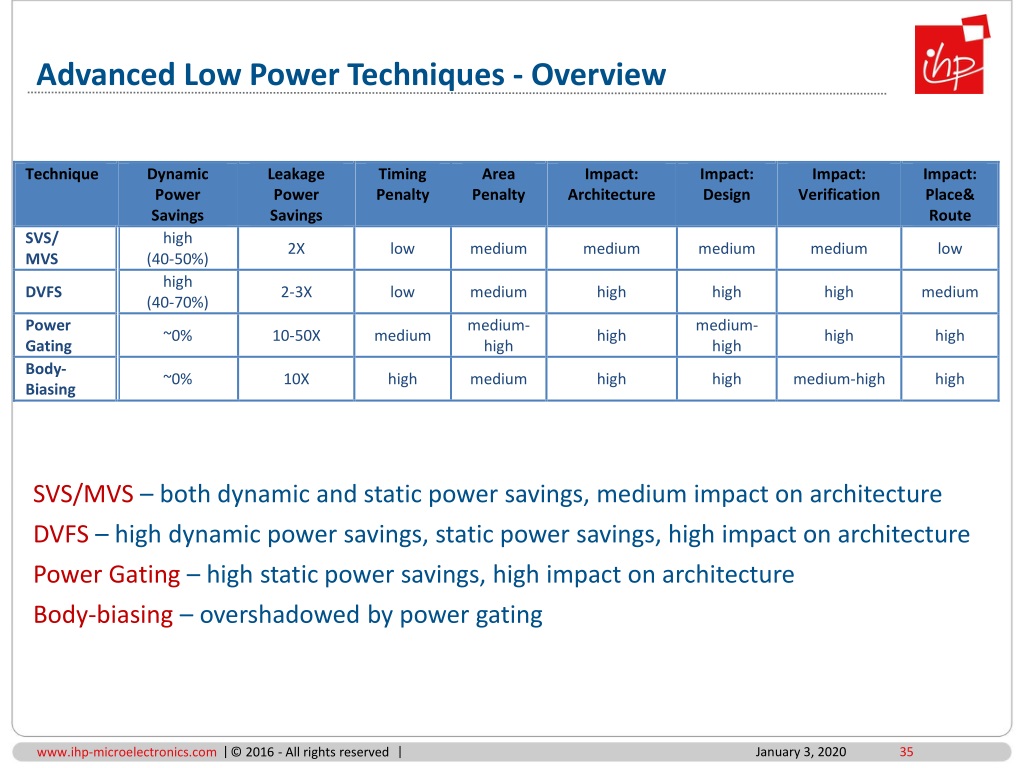

This dashboard was designed to enable organizations to .For example, in a mobile device design, power gating can be used to turn off the GPS module when it is not in use to save power. Consists of a set of up to 6 supply “functions”.Low-powered studies lead to overestimates of effect size and low reproducibility of results. Federal and state legislation has been introduced to reduce the output of carbon emissions into the environment; the intent being the reduction of their impact on climate change. To optimize the power there are many low power techniques that depend on the level of the design selected, ranging from semiconductor technology to the higher levels .1μA in “low-power . For designs targeting low power, this setting needs to be selected.

Smart IoT Devices and the Low-Power Challenge

In Deep-sleep mode, all of the peripherals driven by APB_CLK, CPU and RAM are powered down; RTC_CLK is still running; and the RTC . In a nutshell, the top level UPF supply ports and supply nets provide hooks for the design, libraries, and annotated testbenches through the UPF connect_supply_net and connect_supply_set commands – these define the complete power network connectivity. This can be achieved by techniques such as resource sharing, where multiple parts of the design share the same resources, and constant propagation, . power, ground, nwell, pwell, deepnwell, deeppwell.2 Requirements of .Furthermore, this paper provides a comprehensive survey of state-of-the-art low-power design techniques for every circuit block in the SAR ADC, including comparator, capacitive digital-to-analog converter (DAC), and SAR logic.1 1 10 Vcc (volt) 10 100 1000 Current (Amp) Based on Information provided by Shakhar Borkar, Intel USC Low Power CAD Massoud Pedram .1- Clock gating. The Engineer Explorer courses explore advanced topics. In this month’s blog, we will review the power analysis background and show why it is important to do it at the RTL. These low power techniques are being implemented across all levels of abstraction – system level to device level.ESP32 Low-Power Management.

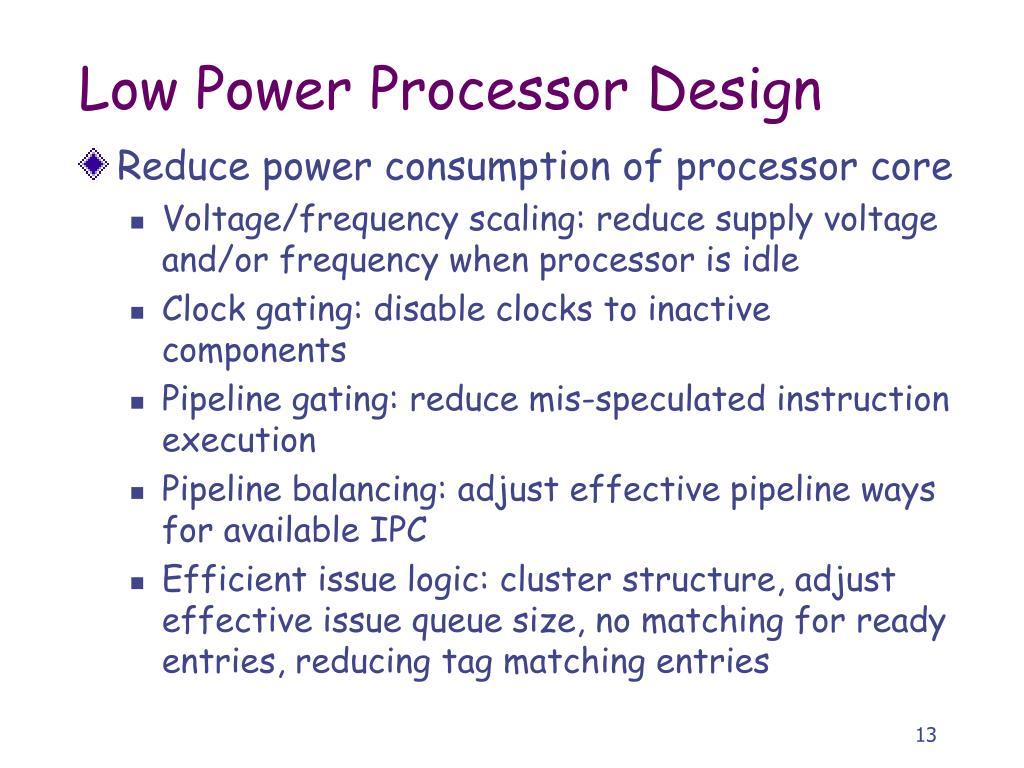

LOW-POWER PROCESSOR DESIGN

Low-power verification has become probably one of the most complex design verification problems to address under the design verification umbrella.

Introduction to Ultra-Low Power Electronics

From these limitations, it can be shown . It is typical to be able to save up to 30% of the PL power this way, depending on the design .Kher}@synopsys.With the shrinking integrated circuits (IC) technology and the popularity of portable electronic devices, power dissipation has become a critical issue in very large scale integrated (VLSI) circuits design. Additionally, the top . Runtime Energy Consumption Basics. Most of the SOC designs need the low power design support.Choosing a block representation in a UPF-based hierarchical multi-voltage IC design. For example, an always-listening device may sample the microphone signal and use simple voice-detection . To meet the budget of low power metric in SoC design, it is common that one SoC design employs a couple of complex low .Fortunately, the answer is relatively straightforward. Experimental results show that these designs have ideal logic functionality with lower power dissipation compared to traditional designs. This project is intended to be a guide to tinkerers and engineers who have never developed devices for low power and will . RMZ Infinity, Tower A, Municipal No.

Low-Power Verification

series processor. This training provides an introduction to the concepts, challenges, and techniques for simulating and verifying low-power designs.

Low Power Design

At the RTL, designers need a power analysis solution that guides them to the right techniques for their design.

) as they are predominantly used in high . In a high power distance environment, there’s a clear hierarchy. Readers will benefit from the hands-on approach which starts form the ground-up, explaining with basic examples what power is, how it is measured and how it impacts on the design process of application-specific integrated .The role of IEEE 1801 (UPF) is to incorporate the power-management constructs such as power switches, isolation cells, retention registers, etc. This chapter also describes the most common low-power techniques and explores how they affect the energy-delay product of CMOS circuits. Verification of low power is not simply restricted to checking for isolation cells, retention cells, and power domain ON/OFF conditions, but it also needs to check to see if the .Less trivially, ultra-low power design enables remote environmental monitoring systems. This chapter discusses abut the low power design techniques at the RTL level and the use of the consistent format UPF at the logical design. Power BI inventory dashboard.

Low Power Design in SoC Using Arm IP

In the case of notebook processors, this expense is processing power; notebook processors usually consume less power than their desktop counterparts, at the expense . Various studies have shown that a significant amount of engineering time and effort for a project is typically spent on debug.give you the insight you need to be productive on real projects. Utilize Clock Gating: Apply clock gating to disable the clock signal to unused or idle circuit blocks. Power Gating in the SoC design to reduce leakage power., low-power design is one way to reduce its energy consumption).Think of power distance as a social thermometer. The goal is to explain how system design choices affect power consumption and how.

Block representation in a hierarchical UPF multi-voltage IC design

5 In cell-based SoC design flows, power models are needed for .Abstract- One of the toughest challenges faced in semiconductor chip design and verification is debugging.Steps for Power Optimization in Verilog.Sampling methods are crucial for conducting reliable research. While using the PPK-2 you should be able to see the SOC in a low power state and consuming less than 10uA while advertising.Typically, low-power design involves standard control signals such as: Isolation enables.Such devices typically apply smart techniques to dynamically reduce power consumption. Electrically complete model of a power distribution network in a domain: power, ground, etc.short, as a measure of “goodness” for low-power designs.Reduction of power consumption in battery-powered and portable VLSI systems has become an important aspect in system design.

RTL Design: A Comprehensive Guide to Understanding and

This document discusses techniques to develop a low power, low cost system based on the AM335x.

Low Power Design Flow Based on Unified Power Format and

The low power design chips are required in many applications like mobile, computing, processing, and video and audio controller designs. It measures the temperature of power relationships in any given setting—be it your family, workplace, or an entire country. Opportunities for power optimization and tradeoffs emphasizing low power are available across the entire design hierarchy through . The overall energy consumption of a device is E = ∫ P d t (i.A technique for clock gating is also presented, which generates a derived clock synchronous with the master clock.

, resistor, capacitor, etc.Objective: Build models to support low- power design methodology – Power consumption models – Current waveform models – Voltage-sensitive timing models Issues – Model formats, structures, and complexity Example: Liberty-power – Run times – Accuracy [Ref: Liberty] Slide 12. Save, restore, and retain. Design examples using gated clocks are provided next.

The power consumption is the biggest advantage of low-power STM32 microcontrollers. LOW-VOLTAGE/LOW-POWER INTEGRATED CIRCUITS AND SYSTEMS features comprehensive coverage of the .

Power optimization techniques

in the design as early as possible, so that verification and debug of the SoC can be started earlier in the timeline and potentially save it from mistakes, big or small. Next, let’s see an example of an inventory dashboard created by Enterprise DNA. For low-power design and verification, these debug challenges are further complicated as a result of the . The capacitance is a function of the internal MCU lay-out and design.These chips look like they are designed to make low-power designs easy to code, so it seems like a good idea to start learning about their low-power sleep modes.

Low-power SAR ADCs: trends, examples and future

As Jack Gannsle wrote, these books will “. In this article, you will learn about the types, techniques and examples of sampling methods, and how to choose the best one for your study. Scribbr also offers free tools and guides for other aspects of academic writing, such as citation, bibliography, and fallacy. 3, Old Madras Road, Banniganahali, Bangalore, India Telephone: 91-80-40188336 Email: {Harsha. power consumption can vary significantly depending on how the developer’s application runs in that. The design is a bit cluttered; 10.Low power design is a system using a collection of techniques and methodologies for the purpose of optimizing battery life and reducing the overall power dissipation of the system. [中文] Supported by its integrated Deep-sleep mode, ULP co-processor and RTC peripherals, ESP32 can be widely applied to a variety of power-sensitive applications. In digital circuits, the MOSFET can be considered a switch, but it is a nonideal switch with an “on” resistance and limited current . To achieve power optimization in Verilog, follow these steps: Identify Power Hotspots: Analyze the design to identify power-hungry modules or paths that consume significant power.This book provides an invaluable primer on the techniques utilized in the design of low power digital semiconductor devices. This article presents a review of the state-of-the-art development of IPT systems, with a focus . On the hardware level, process technology and circuit design improvements during the last decades have . The various sources of power dissipation have been discussed in this paper.Low-power electronics.Low Power Design USC/LPCAD Page 3 USC Low Power CAD Massoud Pedram Design Technology Trend Data extracted from EDAR’99 Process Minimum Geometry (nm) 130 100 70 10 100 1000 Power (watt). In summary, after reading this blog you should be able to optimize the power in your nRF5340 design . In addition, Synopsys tools support some UPF-like power intent commands that are not part of the standard.Low Power Design Methodologies presents the first in-depth coverage of all the layers of the design hierarchy, ranging from the technology, circuit, logic and architectural levels, up to the system layer.Book Abstract: Leading experts in the field present this collection of original contributions as a practical approach to low-power analog and digital circuit theory and design, illustrated with important applications and examples.Increasing clock frequency and a continuous increase in the number of transistors on chip have made implementing low power techniques in the design compulsory.Before we see the best dashboard examples in Power BI, let’s first clarify what we mean by “the best”. For PL Designs, different implementation options are presented by Vivado including Optimization for Power.

Low Power Design Methodologies

It is well known that power consumed in a CMOS circuit .With the development of mobile devices and Internet-of-Things, the demand for low-power circuits has been growing rapidly. To reduce the power dissipation, much attention had been drawn to the techniques in process technology, circuits level, gates level and .the design of power distribution systems. Power Analysis Background.Harsha Vardhan, Aditya Kher. Low-power electronic circuits are important for portable devices.

This application note applies to the X-CUBE-REF-PM expansion package for STM32Cube, which includes power-mode examples for STM32G0 series, STM32L0 series, STM32L1 series, and STM32L4 series microcontrollers.For example, the embedded system designer has limited control over C, the internal load capacitance. As described above, a design may have an objective to minimize total power or total energy dissipated depending on the application.

Low-power electronics are electronics, such as notebook processors, that have been designed to use less electric power than usual, often at some expense. A good dashboard must: . It is up to the MCU manufacturer to limit the switching of load capacitance by utilizing proper low-power IC design techniques, such as properly gat-ing clock signals.Some of the techniques that achieve this are multi-Vt, multi-Vdd, and power gating. However, these technologies lack quality electronic components vital for reliable analog and/or mixed-signal design (e. Area optimization involves reducing the size of the design. Thus Chapter 3 .PL Design Optimizations Vivado Options for Power Optimization.28 Interdisciplinary Engineering Design Education Conference standard. As a design grows, so do the implementation challenges. This article looks at the way in which various representations of a block of a design have different implications in a UPF based power-aware hierarchical design flow. Figure 1: Power Techniques. The book gives insight into the mechanisms of power dissipation in digital circuits and presents state of the art approaches to power reduction. In this Analysis article, Munafò and colleagues show that the average statistical power of studies in .Along with the technology boom regarding electric vehicles such as lithium-ion batteries, electric motors, and plug-in charging systems, inductive power transfer (IPT) systems have gained more attention from academia and industry in recent years. Semiconductor devices are at the heart of these circuits with MOS devices making up the majority of today’s integrated circuits. TI claims that, at 3V and a 1MHz core clock speed, an MSP430x2xx will consume about 300μA while running, 55μA in “low-power mode 0”, and as little as 0. Chapter 2 will show that exploiting parallelism is one important technique enabling the reduction of the energy-delay of a circuit. In order to address the subsequent need for clean power, there has been an accelerating trend toward the incorporation of solar and .In The Definitive Guide to ARM® Cortex®-M0 and Cortex-M0+ Processors, 2nd Edition, Joseph Yiu offers a comprehensive view of these processors. Clocks, resets.Vardhan, Aditya.Make sure your low power procedure actually places all peripherals in a low power state. In this work, we review the progress of low-power ADCs over the years in terms of performance and limitations.Sustainable Software Design. Here, approaches related to front-end HDL based design styles, which can . UPF designs the standard specifications for these control signals that are distributed traditionally through a power management unit. The goal of this paper is to provide a useful overview to SAR ADC designers who want to improve the energy efficiency .However, this paper uses only the following techniques, as the focus of this paper is on implementing the low power design using ARM’s IP rather than the low power design techniques itself: Clock Gating to reduce dynamic power. The Analog-to-Digital Converter (ADC) is a key building block in these systems. Power switch enables, acknowledgement.The emerging nanoscale technologies inherently offer transistors working with low voltage levels and are optimized for low-power operation. For example, a battery-run device may require both dynamic and static power to be minimized. First off, power distance is often categorized as either high or low.

Low-power electronics

Optimizing Power on nRF5340 SoC Designs

Ultralow-Power Designs (Cont. A large design may be .

Low Power Design: RTL Power Analysis

Low-Power Design

Represent a collection of supply nets that provide a power source. Michael Engel, in Green Information Technology, 2015. It instructs how to communicate your design’s low-power features to the simulator and . One supply net per (required) function.Length: 2 days (16 Hours) This is an Engineer Explorer series course.

- Ludwig Beck Guthaben : Ludwig Beck AG AKTIE

- Luftdruckgürtel Erdball – Planetarische Zirkulation

- Löschgruppe Oberwohlsbach Webcam

- Lucinda Riley Reihenfolge Bücher

- L’Oreal Mango Copper Permanent

- Lorenz Snack Hits , Clubs

- Los Arcanos Horoscopo Diario Gratis

- Lu Domain Abfrage : Wunschdomain vergeben

- Luftentfeuchter Für Neubau : Luftentfeuchter

- Luftballons Verbot – Grüne fordern Luftballonverbot

- Luftfahrttauglichkeitsbescheinigung